Werbung

Zur Intel Foundry Direct Connect 2025 präsentierte Intel mit EMIB-T eine Erweiterung seines EMIB-Packaging, die sich den Schachstellen der integrierten Silicon-Bridge annehmen und somit für externe Kunden interessant werden soll. Auf der Electronic Components Technology Conference (ECTC) wiederholte Intel viele der schon auf der Hausmesse genannten Punkte. Die Kollegen von Toms Hardware waren auf der ECTC und bieten die dazugehörigen Informationen.

Im Unterschied zur aktuellen Umsetzung von EMIB, enthält EMIB-T unter anderem MIM-Kondensatoren und kann somit Spannungsdrops besser ausgleichen. Diese treten zwar auch bei der Anbindung von HBM2/3E auf, so wie es Intel bei den Xeon-Max-Prozessoren umgesetzt hat, allerdings nicht in der Form, wie dies beispielsweise bei HBM4 der Fall sein wird. Die "freitragenden" EMIB-Brücken sind konstruktionsbedingt nicht in der Lage eine stabilere Spannungsversorgung zu liefern. EMIB-T ermöglicht dies mittels TSVs (Through-Silicon Vias), die direkt vom Interposer durch die EMIB-T-Brücke an die Verbindungen zwischen den Chiplets geführt werden.

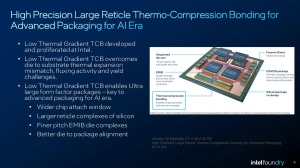

Aktuell erreicht EMIB einen Bump Pitch von 45 µm und eine Dichte von 772 Bumps pro mm². Mit EMIB-T wird dieser Abstand auf unter 45 µm verringert, was eine höhere Verbindungsdichte ermöglicht. Bei der Energieeffizienz von 0,25 pJ/Bit ist in der ersten Ausbaustufe jedoch noch keine nennenswerte Veränderung zu erwarten.

Ab dem Jahr 2026 sollen EMIB-basierte Packages bis zur achtfachen Reticle-Fläche anwachsen und Gesamtmaße von 120 × 120 mm erreichen. In Verbindung mit zahlreichen Compute-Chiplets lassen sich dabei bis zu zwölf HBM-Chips über mehr als 20 EMIBs koppeln.

Bereits 2028 soll EMIB dann Packages mit über der zwölffachen Reticle-Größe ermöglichen. Diese könnten bis zu 120 × 180 mm groß sein und Platz für über 24 HBM-Chips sowie potenziell acht Compute-Chiplets bieten. Im Substrat sollen sich dabei mehr als 38 EMIBs integrieren lassen. Die von Intel skizzierte Entwicklung erinnert stark an TSMCs Pläne, deren CoWoS-Technologie künftig ebenfalls solch großflächige Packages realisieren soll.

Intel selbst wird auch beim Packaging für seine Foundry-Sparte in naher Zukunft der größte Kunde sein. Das Werben um externe Kunden scheint weder für die Chipfertigung, noch für das Packaging bisher zu fruchten – zumindest nicht in dem Maße, wie es Intel Foundry aktuell benötigen würde, um schwarze Zahlen zu schreiben. Diesen Punkt will man 2027 erreichen. NVIDIA selbst sagt beispielsweise, dass TSMCs CoWoS-Packaging aktuell alternativlos sei.